## The RHL-BEADLE Project

Version 1.0

An Introductory Digital Logic Curriculum Using Remotely Accessible FPGA Lab

### **RHL-BEADLE Team:**

#### Authors:

Prof. Rania Hussein, University of Washington Florence Atienza, University of Washington

#### **Testers:**

Justine Bailey, Intel Corporation Cinthya Rosales, Intel Corporation Kaylee Lam, University of Washington

#### **Developers:**

Pablo Orduna, LabsLand Luis Rodriguez-Gil, LabsLand

## Lab 0: GETTING STARTED

The University of Washington | The Remote Hub Lab | Last Revised: March 2022

## Summary

This lab helps students install and become familiar with the technology tools they need to complete the Remote Hub Lab's introductory digital logic lab series. Material includes making an account on the LabsLand platform and downloading Quartus and ModelSim.

## Table of Contents

| About the LabsLand Platform               | 2 |

|-------------------------------------------|---|

| Description                               | 2 |

| For Instructors                           | 2 |

| For Students                              | 2 |

| Downloading Quartus and ModelSim          | 3 |

| Getting the Quartus and ModelSim Software | 3 |

| Creating Your First Quartus Project       | 3 |

## About the LabsLand Platform

#### Description

LabsLand is an online platform where students around the world can access remote hardware laboratories. For the purposes of this introductory digital logic lab series from the Remote Hub Lab (RHLab), LabsLand provides virtual access to real remote hardware through the University of Washington's Electrical and Computer Engineering department.

#### For Instructors

- 1. Go to the following link: <u>https://labsland.com/web/intel/community-colleges</u>.

- 2. Follow the instruction prompts on your screen to create a group for your students.

#### For Students

- 1. Wait for a link from your instructor to join your LabsLand group. DO NOT ACCESS THE LINK ABOVE, WHICH IS FOR INSTRUCTORS ONLY.

- 2. When you are able to login using the link from your instructor, you should be able to see a dashboard which includes three LabsLand laboratories: 1) Digital Trainer, 2) Boole, and 3) Intel DE1\_SoC.

## Downloading Quartus and ModelSim

#### Getting the Quartus and ModelSim Software

The designs and simulations in this lab series will be done through Quartus and ModelSim software, respectively. We will use these tools beginning in Lab 4.

If you are using a Windows machine, you can install the software for free by following these steps:

- 1. Go to https://fpgasoftware.intel.com/?edition=lite.

- 2. Download the free web edition and install it. Note that you will have to register to be able to download the software.

- a. Make sure you Select Edition "Lite" and Select Release "17.0".

- b. Download the 5.8 GB tar file under the "Combined files" tab.

- c. Extract the tar file using a program like 7-zip.

- d. Run the QuartusLiteSetup-17.0-windows.exe file.

- e. When it asks for the components to install, make sure you select each of these:

- Quartus Prime Lite Edition (Free)

- Devices: Cyclone V

- ModelSim: Intel FPGA Starter Edition (Free)

- 3. When the software is done downloading, make sure to install the USB blaster driver.

- 4. Run Quartus next, and if asked about licensing just run the software (we use the free version, so no license required).

In the case that you use a Mac, you can install a virtual machine (which allows you to run Windows on a Mac) and proceed with the steps 1-4 above.

#### Creating Your First Quartus Project

Follow the instructions in this video tutorial to set up and create your first Quartus project and directory for future use in Lab 4: <u>https://youtu.be/iLbmSTG7bpA</u>.

## Lab 1: INTRODUCTION TO GATES AND DIGITAL LOGIC

The University of Washington | The Remote Hub Lab | Last Revised: March 2022

## Summary

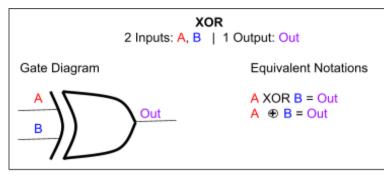

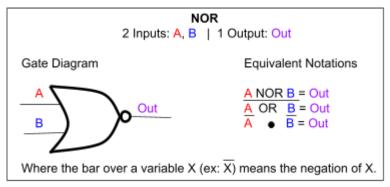

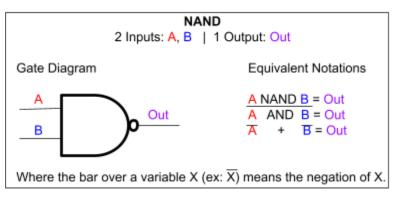

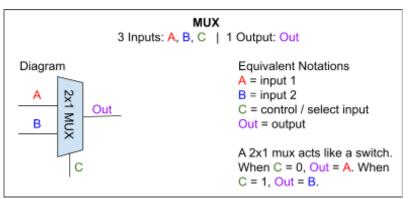

The goal of this lab is to build a foundational understanding of basic logic operators and logic gates. The lab introduces the AND, OR, NOR, XOR, and NAND operators, their corresponding gates, and the functions of a MUX.

## Table of Contents

| Why Should We Study Digital Logic?              | 2  |

|-------------------------------------------------|----|

| Figure 1: An Input/Output (I/O) System          | 2  |

| • • • • • • •                                   |    |

| Logic Operators and Gates                       | 3  |

| Definitions of Basic Operators in Digital Logic | 3  |

| Logic Gates                                     | 3  |

| Figure 2: The "AND" Gate and Operator           | 3  |

| Figure 3: The "OR" Gate and Operator            | 3  |

| Figure 4: The "XOR" Gate and Operator           | 4  |

| Figure 5: The "NOR" Gate and Operator           | 4  |

| Figure 6: The "NAND" Gate and Operator          | 4  |

| Figure 7: The Multiplexor "MUX"                 | 4  |

| LabsLand Activity                               | 5  |

| Premise                                         | 5  |

| Digital Trainer Activity                        | 5  |

| Figure 8: Digital Trainer Diagram               | 5  |

| Instructions                                    | 5  |

| Digital Trainer Observations                    | 6  |

| Digital Trainer Hypotheses and Logic Gates      | 8  |

| Table 1: Digital Trainer Hypotheses             | 8  |

| Looking Ahead                                   | 9  |

| Table 2: Digital Trainer Reasoning              | 9  |

| Reflection and Observations                     | 11 |

|                                                 |    |

## Why Should We Study Digital Logic?

Electronics are powered by electricity and the ability of electricity to be conceptualized into two states: an "off" or an "on" state. Usually, a zero (0) represents the off state (also known as the "false" state), and a one (1) represents the on state (also known as the "true" state).

How can only two representations -- a binary representation -- lead to complex technology? How can electronic devices (phones, computers, televisions, etc.) translate zeros and ones to information and applications? Under their cases, the devices contain fundamental circuits which rely on the basic components of digital logic. As a result, studying these building blocks is a key step in understanding how these devices work.

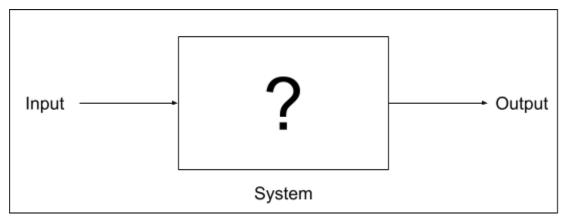

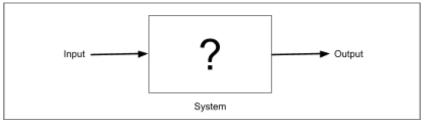

Before analyzing the zeros and ones of digital logic, it is important to understand the concept of inputs vs. outputs. A simple way to visualize this is to first view the inner workings of electronics as a "mystery box" system. We will understand the details later in this curriculum. For now, the key points are the following:

- First, some information enters the box as inputs.

- Then, some transformation happens inside the mystery box system.

- Finally, the changed information exits the system as output.

This input/output (I/O) relationship is shown in Figure 1.

Figure 1: An Input/Output (I/O) System

Building on Figure 1 so the I/O components can be represented in binary format (zeros and ones), we can begin to analyze relationships between electronic components.

## Logic Operators and Gates

#### Definitions of Basic Operators in Digital Logic

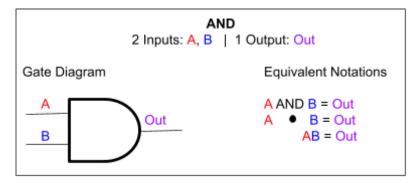

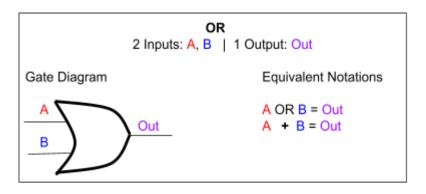

We will focus on five basic operators and one more special piece of hardware (MUX) defined as follows:

- 1. <u>AND</u>: For the output to be true, all inputs "AND-ed" together must be true.

- 2. <u>OR</u>: For the output to be true, at least one of the "OR-ed" inputs must be true.

- 3. <u>NOR</u>: For the output to be true, none of the "NOR-ed" inputs can be true.

- 4. <u>XOR</u>: For the output to be true, the number of true inputs "XOR-ed" together must be odd.

- 5. <u>NAND</u>: For the output to be true, the "NAND-ed" inputs cannot all be true.

- 6. <u>MUX</u>: A switch (control input) chooses between data inputs. Output is equal to the chosen input.

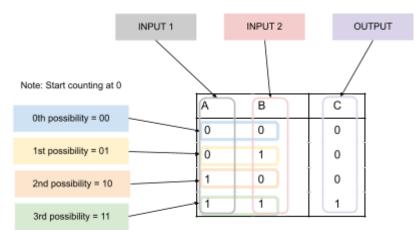

#### Logic Gates

Logic operators can be represented as logic gates. These gates are the hardware or physical components inside electronics. Figures 2-7 illustrate two-input representations of AND, OR, NOR, XOR, and NAND operators and a 3-input representation of the MUX. Accompanied with each figure are "equivalent notations" which preview Boolean Algebra expressions, a topic in "Lab 3: K-Maps and Boolean Algebra." (NOTE: The inverter or NOT gate (not shown) is implied by the bubble on NOR and NAND. It is equivalent to a "negation" denoted by the bar over a variable. The negation of 0 is 1; the negation of 1 is 0.)

Figure 2: The "AND" Gate and Operator

Figure 3: The "OR" Gate and Operator

Figure 5: The "NOR" Gate and Operator

Figure 7: The Multiplexor "MUX"

## LabsLand Activity

#### Premise

The Digital Trainer Activity builds intuition for the AND, OR, NOR, XOR, and NAND operators and the MUX -- the basic building blocks of digital logic. By experimenting with inputs and outputs (I/O) on remote hardware through LabsLand, you will learn how to distinguish relationships between these operators.

Digital Trainer Activity

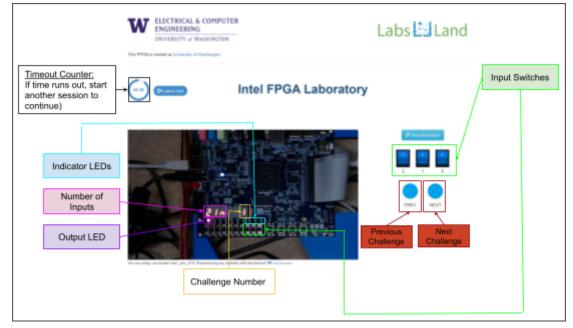

Figure 8: Digital Trainer Diagram

#### Instructions

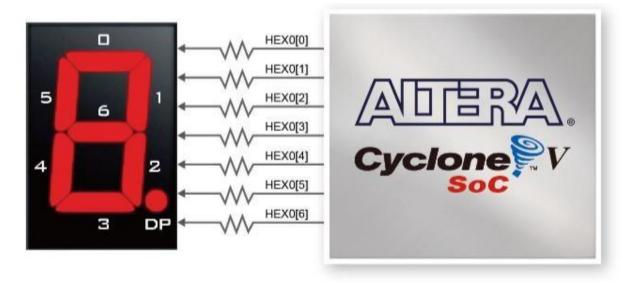

- 1. Familiarize yourself with the LabsLand interface. (A diagram is shown in Figure 8.)

- a. The Field Programmable Gate Array (FPGA) board has 10 challenges pre-programmed.

- b. For each of the 10 challenges, notice that the HEX display (where the red digits and letters are on the FPGA) shows a label for the challenge number and the number of inputs in the challenge.

- c. Locate the blue input switches (Switch2, Switch1, and Switch0) on the right hand side of the screen.

- d. Locate the indicator LEDs (LED2, LED1, LED0) on the right hand side below the HEX display of the challenge number. These LEDs will be lit if their corresponding input switches (Switch2, Switch1, Switch0) are on; the LEDs will be off if their corresponding input switches are off.

- e. Locate the output LED (LEDout) on the left hand side below the HEX display of the number of inputs. This LED will be on if an operator or mux applied to the system inputs results in a "true"; otherwise, the LED will be off.

- f. Use the blue "Prev" and "Next" buttons to go to the previous or the next challenge respectively.

- 2. Using the definitions of basic operators, observe the output LEDs when the input switches are in different combinations of on and off. Note that a switch is "on" when it is flipped "up" and "off" when it is flipped "down."

- 3. Based on your observations, record your initial thoughts in "Digital Trainer Observations" and your guess for the corresponding logic function on display for each challenge in "Digital Trainer Hypotheses and Logic Gates."

#### Digital Trainer Observations

What do you notice about the output LED when the input switches are in different combinations of on and off? Which combinations result in the output LED being on vs. off? Notice that some challenges use 2 inputs, while others use 3 inputs (check the HEX display to find out the number of inputs in the challenge). Hints are given to help you start challenge 1.

- Challenge 1:

- When Switch1 is false and Switch0 is false, LEDOut is \_\_\_\_\_.

- When Switch1 is false and Switch0 is true, LEDOut is \_\_\_\_\_.

- When Switch1 is true and Switch0 is false, LEDOut is \_\_\_\_\_.

- When Switch1 is true and Switch0 is true, LEDOut is \_\_\_\_\_.

- Challenge 2:

- Challenge 3:

- Challenge 4:

- Challenge 5:

- Challenge 6:

- Challenge 7:

- Challenge 8:

- Challenge 9:

- Challenge 10:

#### Digital Trainer Hypotheses and Logic Gates

Based on your observations, what operator do you suppose is on display for each challenge? Use Table 1 to record your guess for what logic function or operator is on display.

| Challenge | How many inputs? | What is | the corres | ponding logic f | function or o | perator? |

|-----------|------------------|---------|------------|-----------------|---------------|----------|

| 1         |                  | AND     | OR         | NAND            | NOR           | XOR      |

| 2         |                  | AND     | OR         | NAND            | NOR           | XOR      |

| 3         |                  | AND     | OR         | NAND            | NOR           | XOR      |

| 4         |                  | AND     | OR         | NAND            | NOR           | XOR      |

| 5         |                  | AND     | OR         | NAND            | NOR           | XOR      |

| 6         |                  | AND     | OR         | NAND            | NOR           | MUX      |

| 7         |                  | AND     | OR         | NAND            | NOR           | MUX      |

| 8         |                  | AND     | OR         | NAND            | NOR           | MUX      |

| 9         |                  | AND     | OR         | NAND            | NOR           | MUX      |

| 10        |                  | AND     | OR         | NAND            | NOR           | MUX      |

| Table | 1: | Digital | Trainer | Hypotheses |

|-------|----|---------|---------|------------|

|-------|----|---------|---------|------------|

Draw the corresponding logic gate or diagram of each of your guesses below.

Challenge 1:

Challenge 2:

Challenge 3:

Challenge 4:

Challenge 5:

- Challenge 6:

- Challenge 7:

Challenge 8:

Challenge 9:

Challenge 10:

## Looking Ahead

Look back at Table 1 where you kept track of your hypotheses. Fill out Table 2 with your guess and a short description of why you chose that operator.

| Challenge | Guess | Why did you choose this operator (1-2 sentences)? |

|-----------|-------|---------------------------------------------------|

| 1         |       |                                                   |

| 2         |       |                                                   |

| 3         |       |                                                   |

| 4         |       |                                                   |

| 5         |       |                                                   |

Table 2: Digital Trainer Reasoning

| 6  |  |

|----|--|

|    |  |

| 7  |  |

| 8  |  |

| 9  |  |

| 10 |  |

These observations will help you in the following lab which introduces a graphic organizer called a "Truth Table". The Truth Table is a mechanism for mapping I/O to zeros and ones which will help you determine if your guesses match the actual operator used in each of the 10 challenges.

## Reflection and Observations

Lab 1 introduced you to logic gates and operators. Reflect on things you found interesting and/or challenging in the space below.

What questions do you still have, if any?

## Lab 2: BINARY NUMBERS AND TRUTH TABLES

The University of Washington | The Remote Hub Lab | Last Revised: March 2022

## Summary

This lab introduces Truth Tables as graphic organizers for digital logic analysis. In this lab you will learn about binary numbers, truth table practice, and an application of truth tables.

## Table of Contents

| Building on Lab 1                             | 2  |

|-----------------------------------------------|----|

| Table 1: Digital Trainer Hypotheses           | 2  |

| Binary Numbers                                | 3  |

| Premise                                       | 3  |

| Figure 1: Base-10 Math                        | 3  |

| Figure 2: Binary (Base-2) Math                | 3  |

| What You Need To Know                         | 4  |

| Table 2: Base-10 and Base-2 Numbers           | 4  |

| Challenge Questions                           | 4  |

| What is a Truth Table?                        | 5  |

| Figure 3: A Blank Truth Table                 | 5  |

| Figure 4: A Truth Table with Data             | 5  |

| Application                                   | 6  |

| Figure 5a: Digital Trainer Blank Truth Tables | 6  |

| Figure 5b: Digital Trainer Blank Truth Tables | 7  |

| Recognizing Patterns                          | 8  |

| Figure 6: Digital Trainer Truth Tables        | 8  |

| Table 3: Truth Table Reasoning                | 9  |

| Reflection and Observations                   | 11 |

## Building on Lab 1

In the previous lab, we covered digital logic operators and gates including AND, OR, NOR, XOR, NAND, and MUX. If you recall, inputs and outputs can be represented as zeros and ones. This lab will allow you to check your intuition about the Digital Trainer's 10 Challenges with zeros and ones organized by a Truth Table.

OPTIONAL: If it is helpful for you, copy your guesses from Lab 1's Table 1 to this lab's Table 1 for easy access. Otherwise, have your answers from Lab 1 readily available to you throughout this lab.

| Challenge | How many inputs? | What is the corresponding logic function or operator? |    |      |     | perator? |

|-----------|------------------|-------------------------------------------------------|----|------|-----|----------|

| 1         |                  | AND                                                   | OR | NAND | NOR | XOR      |

| 2         |                  | AND                                                   | OR | NAND | NOR | XOR      |

| 3         |                  | AND                                                   | OR | NAND | NOR | XOR      |

| 4         |                  | AND                                                   | OR | NAND | NOR | XOR      |

| 5         |                  | AND                                                   | OR | NAND | NOR | XOR      |

| 6         |                  | AND                                                   | OR | NAND | NOR | MUX      |

| 7         |                  | AND                                                   | OR | NAND | NOR | MUX      |

| 8         |                  | AND                                                   | OR | NAND | NOR | MUX      |

| 9         |                  | AND                                                   | OR | NAND | NOR | MUX      |

| 10        |                  | AND                                                   | OR | NAND | NOR | MUX      |

#### Table 1: Digital Trainer Hypotheses

## **Binary Numbers**

#### Premise

Before we introduce Truth Tables, we need a basic understanding of binary numbers. Numbers are binary if they use "base-2" arithmetic. This means every digit in a number can only be a 0 or a 1; there are only two possibilities. In regular arithmetic, every digit in a number can be a 0, 1, 2, 3, 4, 5, 6, 7, 8, or 9. These 10 possibilities for each digit mean we use "base-10" arithmetic in everyday life. Electronics, however, are much more simplistic, so a one-digit number like 8 in base-10 is equivalent to 1000 in binary. How did this arise?

Let's start with base-10 numbers. Base-10 numbers are made up of digits. The rightmost digit is the "ones" place. Moving left, the place increases by a factor of 10. Take 125 for example.

| NAME              | "Hundred's<br>Place"   | "Ten's<br>Place"         | "One's<br>Place"         |                                 |

|-------------------|------------------------|--------------------------|--------------------------|---------------------------------|

| EXAMPLE<br>NUMBER | <u>1</u>               | <u>2</u>                 | <u>5</u>                 | (base-10)                       |

| LOCATION          | 2nd<br>blank           | 1st<br>blank             | 0th<br>blank             |                                 |

| BASE MEANING      | 10 <sup>2</sup>        | 10 <sup>1</sup>          | 10 <sup>0</sup>          |                                 |

| ARITHMETIC        | (1 x 10 <sup>2</sup> ) | + (2 x 10 <sup>1</sup> ) | ) + (5 x 10 <sup>0</sup> | <sup>0</sup> ) = 125 in base-10 |

Figure 1: Base-10 Math

Figure 1 shows the arithmetic value of 125 is preserved if we view 125 as having three sub-locations (0th blank, 1st blank, and 2nd blank). Knowing 125 is base-10, we can break down the number by its one's, ten's, and hundred's places. We can think of binary numbers in the same way. Take 1000 in Figure 2, and note how each digit can only be zero or one.

| NAME              | "Eight's<br>Place"      | "Four's<br>Place"          | "Two's<br>Place"           | "One's<br>Place"        |              |

|-------------------|-------------------------|----------------------------|----------------------------|-------------------------|--------------|

| EXAMPLE<br>NUMBER | <u>1</u>                | <u>0</u>                   | <u>0</u>                   | <u>0</u>                | (base-2)     |

| LOCATION          | 3rd<br>blank            | 2nd<br>blank               | 1st<br>blank               | 0th<br>blank            |              |

| BASE MEANING      | 2 <sup>3</sup>          | 2 <sup>2</sup>             | 2 <sup>1</sup>             | 2 <sup>0</sup>          |              |

| ARITHMETIC        | (1 x 2 <sup>3</sup> ) + | +(0 x 2 <sup>2</sup> ) + ( | 0 x 10 <sup>1</sup> ) + (0 | 0 x 10 <sup>0</sup> ) = | 8 in base-10 |

#### Figure 2: Binary (Base-2) Math

We can see that base-10 and binary numbers can be understood similarly. Binary digits are incremented by powers of two, whereas base-10 digits are incremented by powers of ten.

What You Need To Know

For the purposes of this lab, you should be able to recognize and write out small binary numbers equivalent to 0-15 in base-10. To get you started, Table 2 lists the binary equivalents of the numbers 0-9.

| BASE-10 | BASE-2 (BINARY) |

|---------|-----------------|

| 0       | 0               |

| 1       | 1               |

| 2       | 10              |

| 3       | 11              |

| 4       | 100             |

| 5       | 101             |

| 6       | 110             |

| 7       | 111             |

| 8       | 1000            |

| 9       | 1001            |

#### Table 2: Base-10 and Base-2 Numbers

#### Challenge Questions

To test your understanding, find the binary equivalents of the numbers 11, 12, and 15. Hint: find the largest powers of 2which fit in the number.

- 11 =

- 12 =

- 15 =

Find the base-10 equivalents of these numbers. Hint: each digit corresponds to a power of 2.

- 1010 =

- 1101 =

- 1110 =

## What is a Truth Table?

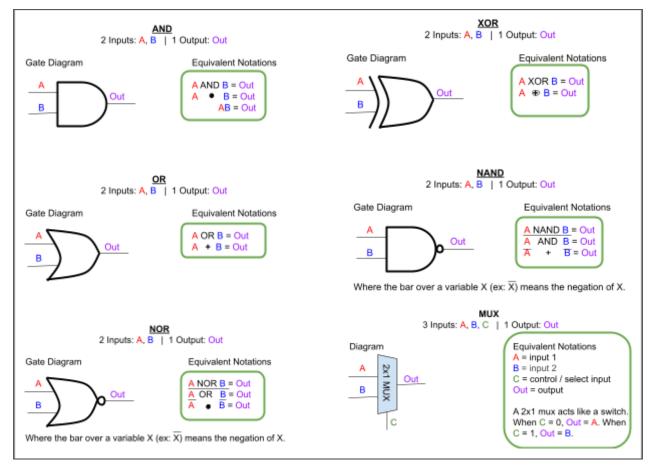

Truth Tables are graphic organizers for keeping track of patterns between the inputs and outputs. Remember that "1" represents "on" and "0" represents "off."

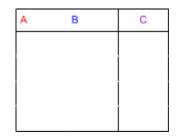

The general form is a T-chart with inputs on the left and outputs on the right. The labels are located at the top of the T-chart, specifying the name of input and output signals. A blank Truth Table with two input signals, A and B, and one output signal C is depicted in Figure 3.

Figure 3: A Blank Truth Table

The information in a Truth Table represents whether the signal was true/on (shown by a 1) or false/off (shown by a 0). Given x inputs, there are  $2^x$  entries of outputs in the Truth Table. The Truth Table inputs correspond to binary numbers, with 0 at the top and  $(2^x - 1)$  at the bottom. Figure 4 shows a color-labeled diagram of each column and row in a Truth Table with sample data.

Figure 4: A Truth Table with Data

Notice that, because we have two inputs, there are  $2^2 = 4$  possible combinations of zeros and ones. Counting in binary, that means the left side of the Truth Table goes from 00 to 11 (0 to 3 in base-10). The right side represents the result of each possibility. In this case, the output was only true when both input signals were on. All other cases -- A and B both off (00), A off and B on (01), A on and B off (10) -- resulted in false outputs.

## Application

Figures 5a-b have 10 blank Truth Tables, 1 for each of the 10 challenges you observed in Lab 1. For the best learning experience, do not look at Figure 6 until you complete Figures 5a-b.

- For each row (an input combination), record the output as a 1 (for on) or 0 (for off).

- Use the output information to guess/verify what the corresponding operator is: AND, OR, NAND, NOR, XOR, and MUX.

- Refer back to the Digital Trainer activity in LabsLand as needed. Also, refer to the definitions for these operators in Lab 1. Your guess can be the same or different from your guess in Lab 1.

- Note that some of the Truth Tables have the input signals filled in as hints; for the others, you must complete all the columns.

#### Challenge 1

Operator:

| SW1 | SW0 | LEDout |

|-----|-----|--------|

| 0   | 0   |        |

| 0   | 1   |        |

| 1   | 0   |        |

| 1   | 1   |        |

### Challenge 3

Operator:

| SW1 | SW0 | LEDout |

|-----|-----|--------|

|     |     |        |

|     |     |        |

|     |     |        |

|     |     |        |

#### Challenge 2

Operator:

| SW1 | SW0 | LEDout |

|-----|-----|--------|

| 0   | 0   |        |

| 0   | 1   |        |

| 1   | 0   |        |

| 1   | 1   |        |

### Challenge 4

Operator:

| SW1 | SW0 | LEDout |

|-----|-----|--------|

|     |     |        |

|     |     |        |

|     |     |        |

|     |     |        |

Figure 5a: Digital Trainer Blank Truth Tables

#### Challenge 5

#### Operator:

Challenge 8

Operator:

| SW1 | SW0 | LEDout |

|-----|-----|--------|

|     |     |        |

|     |     |        |

|     |     |        |

|     |     |        |

## Challenge 6

Operator:

| SW2 | SW1 | SW0 | LEDout |

|-----|-----|-----|--------|

| 0   | 0   | 0   |        |

| 0   | 0   | 1   | ĺ      |

| 0   | 1   | 0   |        |

| 0   | 1   | 1   |        |

| 1   | 0   | 0   |        |

| 1   | 0   | 1   |        |

| 1   | 1   | 0   |        |

| 1   | 1   | 1   |        |

#### Operator: SW2 SW1 SW0 LEDout 0 0 0 0 0 1 0 0 1 0 1 1 1 0 0 1 0 1 0 1 1 1

| SW2 | SW1 | SW0 | LEDout |

|-----|-----|-----|--------|

|     |     |     |        |

| -   |     |     | -      |

|     |     |     |        |

|     |     |     |        |

| -   |     |     |        |

|     |     |     |        |

|     |     |     |        |

| -   |     |     |        |

|     |     |     |        |

|     |     |     |        |

#### Challenge 9 Operator:

| SW2 | SW1 | SW0 | LEDout |

|-----|-----|-----|--------|

|     |     |     |        |

|     |     | Î   |        |

|     |     | Ì   |        |

|     |     | ļ   |        |

|     |     | Ì   |        |

|     |     | ļ   |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

# Figure 5b: Digital Trainer Blank Truth Tables

#### Challenge 10

1

Challenge 7

Operator:

1

| SW2 | SW1 | SW0 | LEDout |

|-----|-----|-----|--------|

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     | -   |        |

|     |     |     |        |

|     |     | -   |        |

|     |     |     |        |

|     |     |     |        |

|     |     | 7   |        |

## **Recognizing Patterns**

Figure 4 illustrates 10 Truth Tables for the 10 challenges you observed in LabsLand. For each Truth Table, the corresponding operator for the challenge is given.

| Challenge | 1: NO | R |

|-----------|-------|---|

|-----------|-------|---|

| SW1 | SW0 | LEDout |

|-----|-----|--------|

| 0   | 0   | 1      |

| 0   | 1   | 0      |

| 1   | 0   | 0      |

| 1   | 1   | 0      |

| SW1 | SW0 | LEDout |

|-----|-----|--------|

| 0   | 0   | 0      |

| 0   | 1   | 0      |

| 1   | 0   | 0      |

| 1   | 4   | 4      |

Challenge 2: AND

| SW1 | SW0 | LEDout |

|-----|-----|--------|

| 0   | 0   | 0      |

| 0   | 1   | 1      |

| 1   | 0   | 1      |

| 1   | 1   | 0      |

|     |     |        |

| SW1 | SW0 | LEDout |

|-----|-----|--------|

| 0   | 0   | 1      |

| 0   | 1   | 1      |

| 1   | 0   | 1      |

| 1   | 1   | 0      |

Challenge 4: NAND

Challenge 5: OR

| SW1 | SW0 | LEDout |

|-----|-----|--------|

| 0   | 0   | 0      |

| 0   | 1   | 1      |

| 1   | 0   | 1      |

| 1   | 1   | 1      |

| Challenge  | 6: MUX       |

|------------|--------------|

| Grinnerige | o de interne |

| SW2 | SW1 | SW0 | LEDout |

|-----|-----|-----|--------|

| 0   | 0   | 0   | 0      |

| 0   | 0   | 1   | 1      |

| 0   | 1   | 0   | 0      |

| 0   | 1   | 1   | 1      |

| 1   | 0   | 0   | 0      |

| 1   | 0   | 1   | 0      |

| 1   | 1   | 0   | 1      |

| 1   | 1   | 1   | 1      |

Challenge 7: OR

Challenge 3: XOR

| Challenge | 8: | NAND |

|-----------|----|------|

|-----------|----|------|

| SW2 | SW1 | SW0 | LEDout |

|-----|-----|-----|--------|

| 0   | 0   | 0   | 1      |

| 0   | 0   | 1   | 1      |

| 0   | 1   | 0   | 1      |

| 0   | 1   | 1   | 1      |

| 1   | 0   | 0   | 1      |

| 1   | 0   | 1   | 1      |

| 1   | 1   | 0   | 1      |

| 1   | 1   | 1   | 0      |

Challenge 9: NOR

| SW2 | SW1 | SW0 | LEDout |

|-----|-----|-----|--------|

| 0   | 0   | 0   | 1      |

| 0   | 0   | 1   | 0      |

| 0   | 1   | 0   | 0      |

| 0   | 1   | 1   | 0      |

| 1   | 0   | 0   | 0      |

| 1   | 0   | 1   | 0      |

| 1   | 1   | 0   | 0      |

| 1   | 1   | 1   | 0      |

|     |     |     |        |

| Challenge | 10:7 | AND |

|-----------|------|-----|

| Grianenge | 10.7 |     |

| SW2 | SW1 | SW0 | LEDout |

|-----|-----|-----|--------|

| 0   | 0   | 0   | 0      |

| 0   | 0   | 1   | 0      |

| 0   | 1   | 0   | 0      |

| 0   | 1   | 1   | 0      |

| 1   | 0   | 0   | 0      |

| 1   | 0   | 1   | 0      |

| 1   | 1   | 0   | 0      |

| 1   | 1   | 1   | 1      |

Figure 6: Digital Trainer Truth Tables

1 0 0 1 1 1 1 1

Compare your Truth Tables in Figures 5a-5b the Truth Tables in Figure 6. If your guess matches, compare your initial reasoning (before learning about Truth Tables) to the Truth Table process. If the tables do not match, revisit LabsLand and double check the system behavior. Describe what you observe in Table 3.

| Challenge | Guess | Did your guess match the operator? Why or why not? (1-2 sentences) |

|-----------|-------|--------------------------------------------------------------------|

| 1         |       |                                                                    |

| 2         |       |                                                                    |

| 3         |       |                                                                    |

| 4         |       |                                                                    |

| 5         |       |                                                                    |

| Tabla | 2. | Truth | Table | Peasoning |

|-------|----|-------|-------|-----------|

| lable | Э. | muun  | Table | Reasoning |

| 6  |  |

|----|--|

|    |  |

| 7  |  |

| 8  |  |

| 9  |  |

| 10 |  |

The reflection and Truth Tables you completed will be helpful in our transition to Boolean Algebra and K-Maps in the following lab. Understanding Truth Tables as graphic organizers will help you derive and represent relationships from observed I/O.

## **Reflection and Observations**

Lab 2 introduced you to Truth Tables and binary numbers. Reflect on the new topics and the things you found interesting and/or challenging in the space below.

What questions do you still have, if any?

## Lab 3: BOOLEAN ALGEBRA AND K-MAPS

The University of Washington | The Remote Hub Lab | Last Revised: March 2022

## Summary

This lab introduces the concept of Karnaugh Maps (K-Maps), a graphic organizer method which converts Truth Tables into Boolean algebra equations or expressions. In this lab you will learn about Boolean algebra, K-Maps, and practice with an application on LabsLand.

## Table of Contents

| What is Boolean Algebra?                                         | 3  |

|------------------------------------------------------------------|----|

| Boolean Algebra Background                                       | 3  |

| Figure 1: Operators and Gate Diagrams                            | 3  |

| Rules to Remember                                                | 4  |

| Figure 2: Boolean Algebra Identities                             | 4  |

| Figure 3: Boolean Algebra Laws                                   | 5  |

| Boolean Algebra Practice                                         | 6  |

| What is a K-Map?                                                 | 7  |

| Karnaugh Map Background                                          | 7  |

| Figure 4: Blank K-Maps                                           | 7  |

| Figure 5: K-Map with Sample Data                                 | 7  |

| Figure 6: Input Combinations Mapped to K-Map Grid Squares        | 8  |

| Figure 7: Truth Table to K-Map Conversion                        | 9  |

| Simplifying K-Maps                                               | 10 |

| Figure 8: Forming Groups on K-Maps (2-Input Example)             | 10 |

| Figure 9: Forming Groups on K-Maps (3-Input Example)             | 10 |

| Figure 10: Truth Table with Don't Cares and K-Map Simplification | 11 |

| Summary of K-Map Rules                                           | 12 |

| Figure 11: Input Combinations Mapped to K-Map Grid Squares       | 12 |

| Figure 12: Maximized vs. Non-Maximized K-Maps                    | 12 |

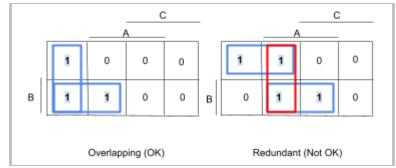

| Figure 13: Overlapping vs. Redundant K-Map Groups                | 13 |

| Practice: Truth Table to K-Map to Boolean Expression             | 14 |

| K-Maps with the Digital Trainer                                  | 15 |

| Table 1: Digital Trainer Challenge 1                             | 15 |

| Table 2: Digital Trainer Challenge 2                             | 15 |

| Table 3: Digital Trainer Challenge 3                             | 15 |

| Table 4: Digital Trainer Challenge 4                             | 16 |

| Table 5: Digital Trainer Challenge 5                  | 16 |

|-------------------------------------------------------|----|

| Table 6: Digital Trainer Challenge 6                  | 16 |

| Table 7: Digital Trainer Challenge 7                  | 17 |

| Table 8: Digital Trainer Challenge 8                  | 17 |

| Table 9: Digital Trainer Challenge 9                  | 18 |

| Table 10: Digital Trainer Challenge 10                | 18 |

| Exercise on LabsLand                                  | 19 |

| Figure 14: Boole Feature                              | 19 |

| Figure 15: Boole IDE                                  | 19 |

| Figure 16: Boole-Web Welcome Page                     | 20 |

| Figure 17: Blank Statement and Configuration Page     | 20 |

| Figure 18: Statement and Configuration Page with Data | 21 |

| Figure 19: Statement and Configuration Page with Data | 21 |

| Figure 20: Boole-Web Truth Table with Data            | 22 |

| Figure 21: Boole-Web K-Map Page                       | 22 |

| Figure 22: Solved K-Maps in Boole-Web                 | 23 |

| Figure 23: Circuit Schematics in Boole-Web            | 23 |

| Recognizing Patterns                                  | 24 |

| Table 11: K-Map Reasonings                            | 24 |

| Looking Ahead                                         | 25 |

| Reflection and Observations                           | 26 |

**Reflection and Observations**

## What is Boolean Algebra?

#### Boolean Algebra Background

Operators are the building blocks of digital logic because they relate input signals to the appropriate output signal(s). Recall from Lab 1 that examples of these operators or hardware are AND, OR, NOR, XOR, NAND, and MUX. While the "word" form of these operators is helpful for understanding their meaning, there is a simpler way to articulate the relationship between signals. To express all the information in a Truth Table in a concise way, Boolean algebra uses regular arithmetic symbols like '+' to represent OR and '•' to represent AND

Lab 1 provided a summary of operators and gate diagrams, depicted here by Figure 1.

#### Figure 1: Operators and Gate Diagrams

The right-hand columns labeled "Equivalent Notations" and boxed in **green** are examples of Boolean Algebra expressions. Recall that these gates are physical components in electronic circuits, so it is ideal that we minimize the complexity of gates in our operations. In particular, Boolean Algebra can help us reduce the number of inputs to the gates and the number of gates.

#### Rules to Remember

Figures 2-3 list some important Boolean algebra identities and laws, along with an explanation for how to think about the relationship. Recall that a variable with a bar over it means the "negation" or the "opposite" of the variable. For example,  $\overline{X}$  means 'not X', so if X is true,  $\overline{X}$  is false. Conversely, if X is false,  $\overline{X}$  is true. Key identities that may be new to you are highlighted in green. Notice that many identities and laws are similar to the rules of regular algebra.

"OR" (+) Identities  $\rightarrow$  When is (X OR 0) true? **Ans**: 0 can never be true. Answer is only when **X** is true. X + 0 = X $\rightarrow$  When is (X OR True) true? **Ans**: 1 is always true no matter X. Answer is **1** (all the time). X + 1 = 1 $\rightarrow$  When is (X OR X) true? Ans: We have the same input signal. Answer is only when X is true. X + X = X $\rightarrow$  When is (X OR  $\overline{X}$ ) true? Ans: X and not X are the only possibilities, so at least one of them is true all the time, so the answer is 1.  $X + \overline{X} = 1$ "AND" (•) Identities  $\rightarrow$  When is (X AND True) true? **Ans**: 1 is always true, so the answer depends only on **X**.  $X \bullet 1 = X$  $\rightarrow$  When is (X AND False) true? **Ans**: **0** is always false, no matter X.  $X \bullet 0 = 0$  $\rightarrow$  When is (X AND X) true? **Ans**: Same input signal, so answer is only when **X** is true.  $X \bullet X = XX = X$

$\rightarrow$  When is (X OR  $\overline{X}$ ) true? **Ans**: X and not X are the only possibilities of X, so both cannot be true at the same time. The answer is **0**.

$X \bullet \overline{X} = X\overline{X} = 0$

Figure 2: Boolean Algebra Identities

<u>Laws</u>

## Commutative Laws: $\rightarrow$ Comparing when X OR Y is true is the same as comparing when Y OR X is true. X + Y = Y + X $\rightarrow$ Comparing when X AND Y is true is the same as comparing when Y AND X is true. XY = YXAssociative Laws: $\rightarrow$ Set A = (Y OR Z) = (Y+Z). Set B = (X OR Y) = (X+Y). (X OR A) is the same as (B OR Z). X + (Y + Z) = (X + Y) + Z $\rightarrow$ Set A = YZ. Set B = XY. (X AND A) is the same as (B AND Z). X(YZ) = (XY)Z**DeMorgan's Laws**: $\rightarrow$ Negating an entire operation = negating each signal and changing to the opposite operator. $\overline{(X + Y)} = \overline{X} \bullet \overline{Y}$ $(X \bullet Y) = X + Y$ Absorption Laws: • X + XY = X(1 + Y) = X(1) = XX + XY = X• $XY + X\overline{Y} = X(Y + \overline{Y}) = X(1) = X$ $XY + \overline{X}Y = X$ • $X + \overline{X}Y = X + XY + \overline{X}Y = X + Y(X + \overline{X}) = X + Y(1) = X + Y$ X + XY = X + Y• X(X + Y) = XX + XY = X + XY = X(1 + Y) = X(1) = X. X(X + Y) = X• $(X + Y)(X + \overline{Y}) = XX + X\overline{Y} + XY + Y\overline{Y} = X + X\overline{Y} + XY + 0 = X + XY = X$ $(X + Y)(X + \overline{Y}) = X$ • $(X)(\overline{X} + Y) = X\overline{X} + XY = 0 + XY = XY$ $X(\overline{X} + Y) = XY$ **Distributive Laws:** $\rightarrow$ The AND operator distributes over OR'ed quantities. X(Y + Z) = XY + XZ $\rightarrow (X+Y)(X+Z) = XX + XZ + YX + YZ = X + XZ + XY + YZ = X(1+Z+Y) + YZ = X + YZ$ X + YZ = (X + Y)(X + Z)

Figure 3: Boolean Algebra Laws

Boolean Algebra Practice

What is the simplest form of the expression  $(A + C)(AD + A\overline{D}) + AC$ ? Use the identities and laws in Figures 2-3. (To see examples, refer to the "Absorption Laws" in Figure 3.)

## What is a K-Map?

### Karnaugh Map Background

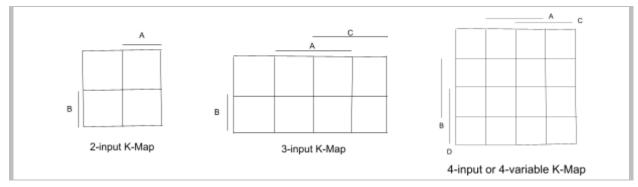

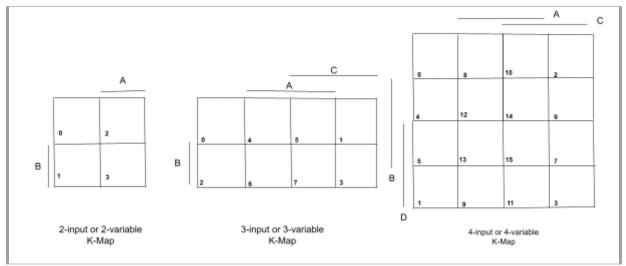

Karnaugh Maps, or K-Maps, are another way of simplifying Boolean expressions. Using a grid-type chart, K-Maps allow you to arrive at a simplified Boolean expression by eliminating redundant variables. The size of the chart depends on the number of inputs, as shown in Figure 4. To understand how K-Maps work, look at the 2-input, 3-input, and 4-input cases in Figure 4.

Figure 4: Blank K-Maps

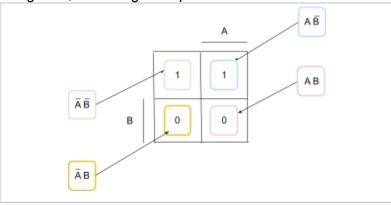

All these K-Map types involve smaller grid squares. Each square represents the output value for an input combination (and thus a row on a Truth Table). For example, imagine a 2-input K-Map. It has labels for its variables written on the perimeter of the chart and marked with a bar for the relevant columns and rows. These labels designate when the inputs are true. Take the K-Map with sample data in Figure 5, assuming the inputs are called 'A' and 'B'.

Figure 5: K-Map with Sample Data

Notice the labels for two inputs, A and B, mark a column and a row respectively. This means the squares under the column labeled A denote when A is true. The left-hand column signifies when A is false. Moreover, the squares in the row aligned with the label B designate when B is true, and the top row designates when B is false. If the output is 'true' when inputs A and B are on, then the corresponding box for 'AB' will contain a 1. In this K-Map, AB is false, so the pink square in the bottom right corner has a 0.

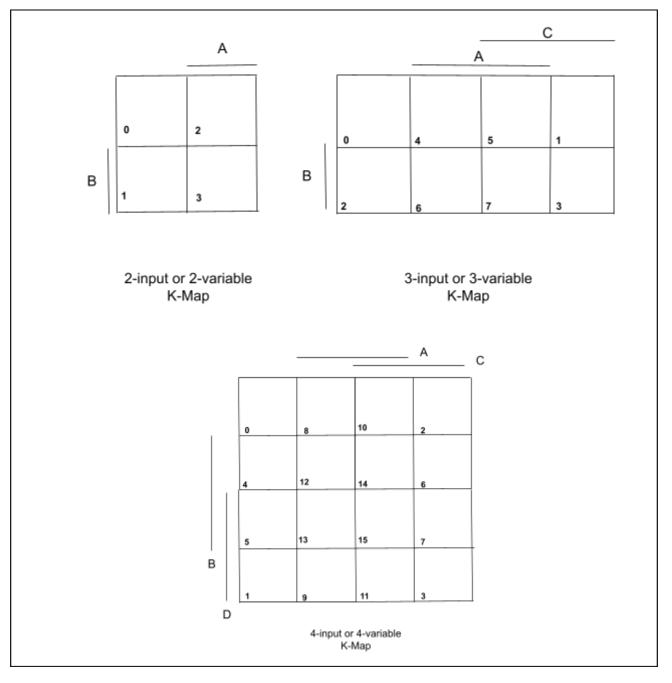

The 3-input and 4-input cases follow the same reasoning. Because each square in a K-Map represents the output of an input combination, we can derive a Truth Table from a K-Map and vice versa. For accuracy, you need to "fill in" a K-Map in a certain order; that's where binary numbers come in. Observe the numbers in the bottom left of the grid squares in each K-Map in Figure 6; they correspond to specific rows (and thus input combinations) on a Truth Table.

Figure 6: Input Combinations Mapped to K-Map Grid Squares

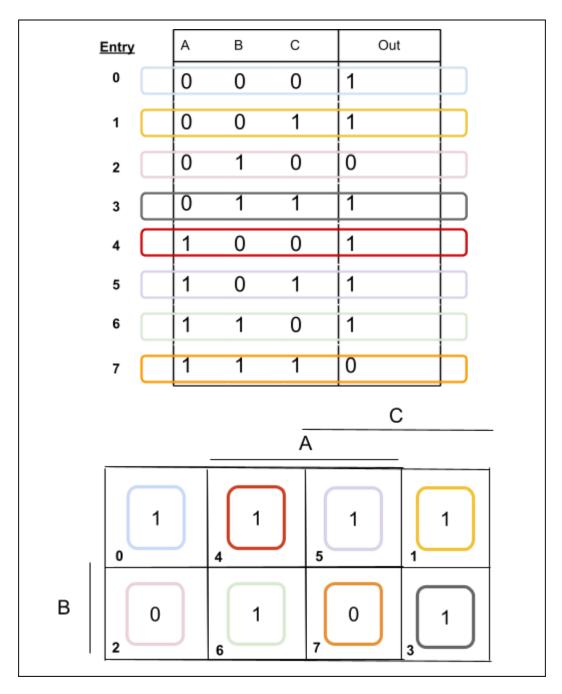

As an example, let's look at the Truth Table and corresponding K-Map in Figure 7.

Figure 7: Truth Table to K-Map Conversion

Notice how the 3-inputs map to labels around the perimeter of the K-Map. Moreover, notice how the nth entry of the Truth Table corresponds to the grid square label in the bottom left corner. This illustrates how, when translating a Truth Table to a K-Map, you should carefully transfer the outputs to the appropriate grid square. This process also applies to translating a K-Map to a Truth Table.

#### Simplifying K-Maps

Now that we know how to understand and write K-Maps from Truth Tables and vice versa, how can we simplify the Boolean algebra? With 2-input, 3-input, and 4-input K-Maps, the trick is to look for groups of adjacent 1s in quantities of one, two, four, eight, or sixteen and group them together. The goal is to maximize the number of 1s in a group, but minimize the number of groups we make. Only the squares encompassed by a group will be included in the expression.

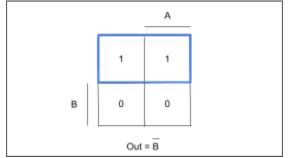

A 2-input example is shown in Figure 8. Notice that the output contains the expression that best describes the group of 1s. In this case, we need an expression for the top row. We notice that the blue group is the region not included by B. As a result, the output of this system is  $\overline{B}$  according to the K-Map.

Figure 8: Forming Groups on K-Maps (2-Input Example)

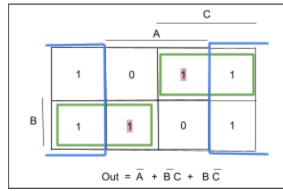

Figure 9 depicts another example with a 3-input K-Map. Note that the simplest expressions may have a group of four which can "go off the grid." This can happen from right-to-left (as shown in Figure 9) or top-to-bottom. Because the bottom left corner 1 and top right corner 1 were already covered by the group of four, we only need to cover the two 1s highlighted in pink. But, we notice that there are adjacent 1s to these lone, uncovered pink 1s. It is important to note that our goal is to simplify, so we would rather have 2-variable terms rather than 3-variable terms. As a result, we allow overlap so lone, uncovered 1s can join a group of two, four, eight, or sixteen.

Figure 9: Forming Groups on K-Maps (3-Input Example)

The result is the sum of all possible groups. In this case, we found three groups so there are three terms added together - the "OR"-ing of all possibilities.

Sometimes, there are Truth Tables (and by extension, K-Maps) with input combinations which are not relevant to the system. For example, assume we have a 4-input Truth Table which has defined behavior for all input combinations except for 5, 10, 11, 12, 13, 14, and 15. In this case, we should put X's in the output column(s) of these input combinations which are irrelevant to the system. One of these X's is called a "Don't Care." This Truth Table example and how to simplify its K-Map is shown in Figure 10.

| А | В | С | D | Out |   |   |           |                                |   |   |

|---|---|---|---|-----|---|---|-----------|--------------------------------|---|---|

| 0 | 0 | 0 | 0 | 1   | 1 |   |           |                                | A | ~ |

| 0 | 0 | 0 | 1 | 0   |   | [ |           |                                |   | C |

| 0 | 0 | 1 | 0 | 1   |   |   |           |                                |   |   |

| 0 | 0 | 1 | 1 | 1   |   | 1 | 1         | x                              | 1 |   |

| 0 | 1 | 0 | 0 | 0   |   |   |           |                                |   | - |

| 0 | 1 | 0 | 1 | x   |   | 0 | x         | x                              | 1 |   |

| 0 | 1 | 1 | 0 | 1   |   |   |           |                                |   |   |

| 0 | 1 | 1 | 1 | 1   |   |   |           |                                |   |   |

| 1 | 0 | 0 | 0 | 1   |   | X | x         | x                              | 1 |   |

| 1 | 0 | 0 | 1 | 1   |   |   |           |                                |   |   |

| 1 | 0 | 1 | 0 | x   | В | 0 | 1         | x                              | 1 |   |

| 1 | 0 | 1 | 1 | x   |   | Ŭ | •         |                                |   |   |

| 1 | 1 | 0 | 0 | x   | D |   |           |                                |   |   |

| 1 | 1 | 0 | 1 | x   |   |   | 0.4 - 4   | 0. 55                          |   |   |

| 1 | 1 | 1 | 0 | x   |   |   | Out = A + | $C + \overline{B}\overline{D}$ |   |   |

| 1 | 1 | 1 | 1 | x   | 1 |   |           |                                |   |   |

Figure 10: Truth Table with Don't Cares and K-Map Simplification

In Figure 10's Truth Table, notice that we "don't care" about the input combinations which are highlighted in yellow, so the output column is marked with X's. These Don't Cares can be treated as '1s' or '0s' if it helps us maximize the number of 1s in a group, but minimize the number of groups we make. This simplification is seen in Figure 10's K-Map. All Don't Cares in the middle two columns can help create non-redundant groups of eight 1s. Consequently, all Don't Cares are assumed to be '1' except for the Don't Care in red underlined.

Summary of K-Map Rules

#### STEP 1: Draw the K-Map.

- 1. Draw a 2x2 square grid (2-input system), a 4x2 square grid (3-input system), or a 4x4 square grid (4-input system).

- 2. Fill in the smaller squares with the outputs from the Truth Table.

Figure 11: Input Combinations Mapped to K-Map Grid Squares

STEP 2: Form groups according to the following rules:

- 1. The goal is to form groups of adjacent 1s.

- 2. Groups must take a square or rectangular shape (no diagonals).

- 3. Groups of 1s can be a power of two in size: one, two, four, eight, or sixteen.

- 4. Maximize the number of 1s in each group, and minimize the number of groups you make. (This may involve Don't Care's.)

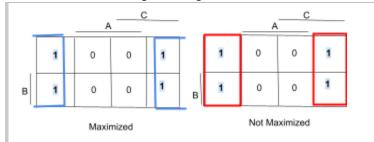

A group is "maximized" when it includes all possible adjacent 1s. The example in Figure 12 shows a maximized group of four vs. two non-maximized pairs. The one on the left is more correct because it maximizes the number of 1s in a group (there are four 1s) and minimizes the number of groups (there is only one group instead of two). Note that going "off the grid" or off the sides of the grid is legal!

Figure 12: Maximized vs. Non-Maximized K-Maps

5. Groups can overlap, but groups cannot be fully redundant; only make groups if there is a 1 that is uncovered/ungrouped.

Figure 13: Overlapping vs. Redundant K-Map Groups

6. You are "done" finding groups when every 1 is part of a maximized group.

In Figure 13, notice that, after finding a pair of ones in the left K-Map (say the pair in the bottom row), there is still a 1 above without a group. Remember that we want to maximize the number of ones in a group and minimize the number of groups, so we would rather have two groups of two 1s rather than one pair and a single 1. As a result, we group the remaining 1 (in the  $\overline{A} \ \overline{B} \ \overline{C}$  position) with the 1 below it. So, we get two groups which overlap.

### STEP 3: Translate into a Boolean expression.

1. Name the groups you found using the labels on the K-Map perimeter.

In the 2-input K-Map, notice that the label 'A' is aligned with the right column and the label 'B' is aligned with the bottom row. Similarly, in the 3-input K-Map, notice that the label 'A' is aligned with the middle four-square region, 'C' is aligned with the right four-square region, and 'B' is aligned with the bottom row.

When naming a group, locate which region(s) contain it and which region(s) do not contain it. For example, look at the pair of ones in the bottom row of the left K-Map in Figure 13. Notice that this group is not contained by C but is contained by B. However, one element of this group is contained by A but the other element is not contained by A. Therefore, we only need B and C to describe the group, and we can name it  $B\overline{C}$  because it is NOT in C and it is in B. Following similar reasoning, the vertical pair in the leftmost column is not contained by A, is not contained by C, and is split over B. Therefore, this group is called  $\overline{A} \overline{C}$ .

2. Add the terms together to arrive at the simplified result.

This works because you are essentially "OR-ing" each possible group together. The simplified result for the left (correct) K-Map in Figure 13 is  $Out = B\overline{C} + \overline{A}\overline{C}$ .

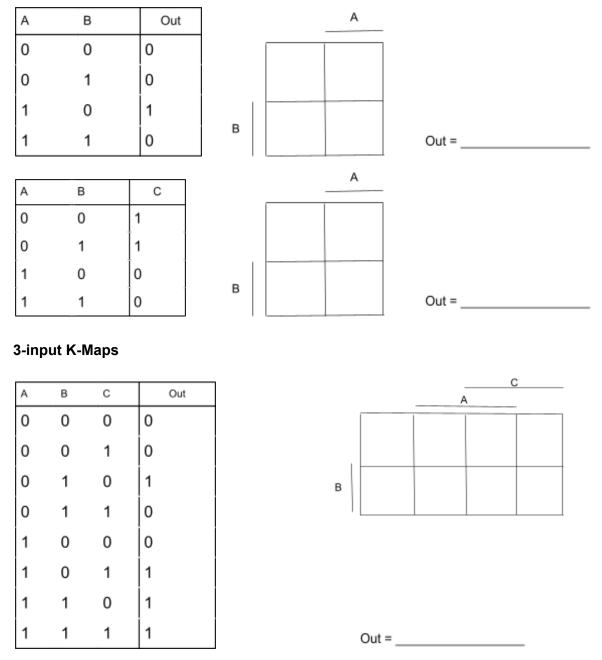

### Practice: Truth Table to K-Map to Boolean Expression

Using the given Truth Tables, draw the corresponding K-Maps and determine the Boolean expression.

#### 2-input K-Maps

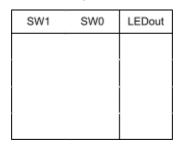

### K-Maps with the Digital Trainer

For each challenge corresponding to the Digital Trainer Activity, do the following:

- 1. Fill in the Truth Table. You can use your answers from Lab 1 or Lab 2.

- 2. Use the Truth Table to make a K-Map.

- 3. Use the K-Map to arrive at a Boolean Expression/Equation.

- 4. Check that the Boolean Equation you arrive at matches the correct operator you found in Lab 1. Remember that there are multiple equivalent representations of the same Boolean relationship. For example,  $\overline{(X + Y)} = \overline{X} \cdot \overline{Y}$  and  $\overline{(X \cdot Y)} = \overline{X} + \overline{Y}$ .

Table 1: Digital Trainer Challenge 1

Boolean Equation: \_\_\_\_\_

#### Table 2: Digital Trainer Challenge 2

Boolean Equation: \_\_\_\_\_

Table 3: Digital Trainer Challenge 3

| SW1 | SW0 | LEDout |

|-----|-----|--------|

|     |     |        |

|     |     |        |

|     |     |        |

|     |     |        |

|     |     |        |

Boolean Equation:

| SW1 | SW0 | LEDout |  |

|-----|-----|--------|--|

|     |     |        |  |

|     |     |        |  |

|     |     |        |  |

|     |     |        |  |

|     |     |        |  |

Boolean Equation: \_\_\_\_\_

Boolean Equation: \_\_\_\_\_

#### Table 5: Digital Trainer Challenge 5

| SW0 | LEDout |

|-----|--------|

|     |        |

|     |        |

|     | ĺ      |

|     |        |

|     | SW0    |

# Table 6: Digital Trainer Challenge 6

| SW2 | SW1 | SW0 | LEDout |

|-----|-----|-----|--------|

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

Boolean Equation: \_\_\_\_\_

Table 7: Digital Trainer Challenge 7

| SW2 | SW1 | SW0 | LEDout |

|-----|-----|-----|--------|

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

Boolean Equation:

Table 8: Digital Trainer Challenge 8

| SW2 | SW1 | SW0 | LEDout |

|-----|-----|-----|--------|

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

Boolean Equation: \_\_\_\_\_

Table 9: Digital Trainer Challenge 9

| SW2 | SW1 | SW0 | LEDout |

|-----|-----|-----|--------|

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

Boolean Equation: \_\_\_\_\_

Table 10: Digital Trainer Challenge 10

| SW2 | SW1 | SW0 | LEDout |

|-----|-----|-----|--------|

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

|     |     |     |        |

Boolean Equation: \_\_\_\_\_

### Exercise on LabsLand

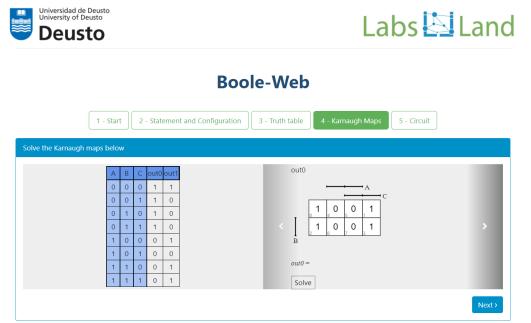

Use the Boole-Web feature on LabsLand to see the whole  $I/O \rightarrow Truth Table \rightarrow K-Map process$ , and verify your answers to Challenges 1-10 from the Digital Trainer Activity. Follow the process detailed in this section to access Boole-Web, and repeat steps 4-10 for each of the challenges.

1. On your LabsLand dashboard, navigate to the "Boole" feature, and click on "Access this lab."

Figure 14: Boole Feature

2. Click on "Access" under "Boole IDE."

| Image: organization of the sector of the |                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Boole IDE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Boole (All FPGAs) |

| Boole IDE with DE1-SoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Boole (All FPGAs) |

| Access >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Access >          |

Figure 15: Boole IDE

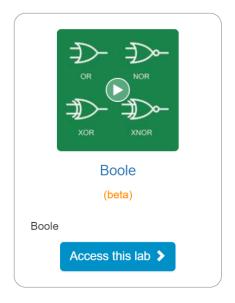

3. You will see the Boole-Web welcome page as shown in Figure 16. Read the intro, and press "Next." You should now see the screen shown in Figure 17.

Figure 17: Blank Statement and Configuration Page

20

- 4. Add a project title and description in the Statement and Configuration Page (Figure 17). This is for documentation purposes.

- 5. Add the inputs and outputs of your system. For example, given a 3-input system with inputs 'A', 'B', and 'C' and 2 outputs 'Out1' and 'Out0', click 'Add input' twice and 'Add output' once. Enter the appropriate input and output names in each blank. Ensure that the topmost name is the rightmost variable in your TruthTable; in this case, that is input C and output out1. Press 'Next' when finished, as depicted in Figure 18.

| le                    |                     | Lab            | 3 Demo                     |                  |                       |                    |  |   |

|-----------------------|---------------------|----------------|----------------------------|------------------|-----------------------|--------------------|--|---|

| Normal \$             | BIU                 | • ≡ ≡          | $\mathcal{I}_{\mathbf{x}}$ |                  |                       |                    |  |   |

| This is an example    | e for the "Verifica | ion Using Labs | Land's Boole-Web           | Feature" section | n in "Lab 3: Boolean. | Voebra and K-Maps' |  |   |

| rno lo un oxampo      |                     | ton Comy Land  | Salidea Doolo-Fred         | reading section  |                       | igeora ana romapo  |  |   |

|                       |                     |                |                            |                  |                       |                    |  |   |

|                       |                     |                |                            |                  |                       |                    |  |   |

|                       |                     |                |                            |                  |                       |                    |  |   |

|                       |                     |                |                            |                  |                       |                    |  |   |

|                       |                     |                |                            |                  |                       |                    |  |   |

|                       |                     |                |                            |                  |                       |                    |  |   |

|                       |                     |                |                            |                  |                       |                    |  |   |

| Inputs and out        | puts                |                |                            |                  |                       |                    |  |   |

| Inputs and out        | puts                |                |                            |                  | Outputs               |                    |  |   |

|                       | puts                |                |                            |                  | Outputs<br>Add out    | put                |  |   |

| Inputs<br>+ Add input | puts                |                |                            |                  | + Add out             | put                |  |   |

| Inputs                | puts                |                |                            | 8                |                       | put                |  | 8 |

#### **Boole-Web**

Figure 18: Statement and Configuration Page with Data

6. You should now see your project description in the top left with a K-Map missing its outputs in the top right. Note how the rows of the K-Map have its inputs auto-filled.

| Boole-                                                                                                              | -Web                                                                                                                                                                                                                                                                                                                                                                                   |       |

|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1 - Start 2 - Statement and Configuration 3 -                                                                       | Truth table 4 - Karnaugh Maps 5 - Circuit                                                                                                                                                                                                                                                                                                                                              |       |

| Fill in the truth table from the statement                                                                          |                                                                                                                                                                                                                                                                                                                                                                                        |       |

| This is an example for the "Verify on LabsLand's Boole-Web Feature" section in "Lab 3: K-Maps and Boolean Algebra". | A         E         c         outBout1           0         0         0         0           0         0         1         0           0         1         0         0           1         0         0         0           1         0         0         0           1         0         0         0           1         1         1         0           1         1         1         0 |       |

|                                                                                                                     | Clear table                                                                                                                                                                                                                                                                                                                                                                            |       |

| Select a formula to display Select a formula to display •                                                           |                                                                                                                                                                                                                                                                                                                                                                                        |       |

|                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                        | Next> |

Figure 19: Statement and Configuration Page with Data

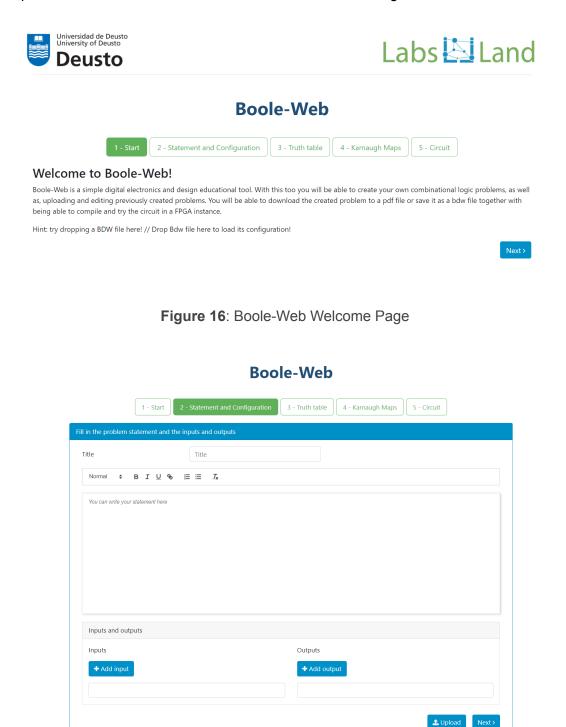

Fill in out0 and out1 according to your observed I/O behaviors. notice the shortcuts below the Truth Table: 'Clear Table', '0' (fill all remaining output rows with 0), '1' (fill all remaining output rows with 1), 'X' (fill all remaining output rows with X which means "Don't Care" - something we'll learn about in Lab 5).

A Truth Table may look like the example in Figure 20. Press 'Next' when finished.

Figure 20: Boole-Web Truth Table with Data

8. You should see a page as shown in Figure 21 with the K-Maps drawn for each of your outputs. Press the left and right arrows highlighted in gray to scroll through the K-Maps.

Figure 21: Boole-Web K-Map Page

9. Press 'Solve' to see the resulting Boolean Expressions from each K-Map. Boole-Web solves the grouping and simplification for you!

| out0                    |               | out1                                                     |  |

|-------------------------|---------------|----------------------------------------------------------|--|

|                         |               | A                                                        |  |

|                         |               |                                                          |  |

|                         | - <b>&gt;</b> |                                                          |  |

| В                       |               | B                                                        |  |

| $out0 = (\overline{A})$ |               | $out1 = (\overline{C} \cdot \overline{B}) + (B \cdot A)$ |  |

| Hide                    |               | Hide                                                     |  |

Figure 22: Solved K-Maps in Boole-Web

10. To see the schematic of gates which are built according to the Boolean expressions found by Boole-Web, press "Next." You should see the screen as shown in Figure 22 with a combination of logic gates for your system.

| Universidad de Deusto<br>University of Deusto<br>Deusto |                               | La                                    | abs 🔄 Land    |

|---------------------------------------------------------|-------------------------------|---------------------------------------|---------------|

|                                                         | Bo                            | oole-Web                              |               |

| 1 - Start                                               | 2 - Statement and Configurati | ion 3 - Truth table 4 - Karnaugh Maps | 5 - Circuit   |

| The logic circuits for the systems are li               | isted below                   |                                       |               |

|                                                         | A⊷_D>−out0                    |                                       |               |

| C Restart                                               | ඵ Download PDF                | Try in Real Hardware                  | 🖺 Save system |

Figure 23: Circuit Schematics in Boole-Web

- 11. Repeat steps 4-10 for each of the Digital Trainer challenges from Labs 1 and 2. Verify that the resulting K-Maps and Boolean equations you found in Tables 1-10 are equivalent to those computed by Boole-Web. Use the "Recognizing Patterns" section in Lab 3 to write down your observations.

- 12. OPTIONAL: Note that Boole-Web has many features which are not covered by this Lab but you are free to explore. If you're curious, under tab "3-Truth table, look at the options under "Select a formula to display." What do you notice for each option? In tab "5-Circuit', check out "Try in Real Hardware." Can you connect signals to I/O on an FPGA to observe real-world behavior? Also, take a look at the "Download PDF" and "Save system" features for easy access outside of LabsLand.

### **Recognizing Patterns**

Compare your K-Maps and Boolean equations in Tables 1-10 to the K-Maps and Boolean Equations computed by Boole-Web. If your guess matches, compare your initial reasoning to Boole-Web's process. If the K-Maps or equations do not match, revisit the LabsLand Digital Trainer and double check the system behavior. Describe what you observe.

Table 11: K-Map Reasonings

| Challenge | Operator<br>Guess | Did your guess match Boole-Web? Why or why not? (1-2 sentences) |

|-----------|-------------------|-----------------------------------------------------------------|

| 1         |                   |                                                                 |

|           |                   |                                                                 |

| 2         |                   |                                                                 |

| 3         |                   |                                                                 |

| 4         |                   |                                                                 |

| 5         |                   |                                                                 |

| 6  |  |

|----|--|

| 7  |  |

| 8  |  |

| 9  |  |

| 10 |  |

### Looking Ahead

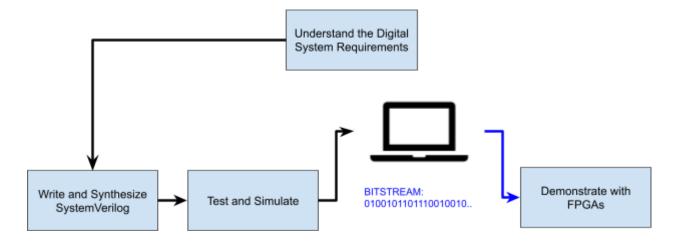

This lab wraps up the fundamental topics covered in this lab series for understanding digital logic. Now that you know about Boolean Algebra and K-Maps, we can look into applying it in real systems. The following lab will shift to introducing computer tools which will help us visualize the digital logic concepts we've been discussing. Future labs will call on all the foundational knowledge (Boolean Algebra, K-Maps, Truth Tables, Binary Numbers, Gates, and Operators) we've built so far.

### Reflection and Observations

Lab 3 introduced you to K-Maps and Boolean algebra. Reflect on the new topics and the things you found interesting and/or challenging in the space below.